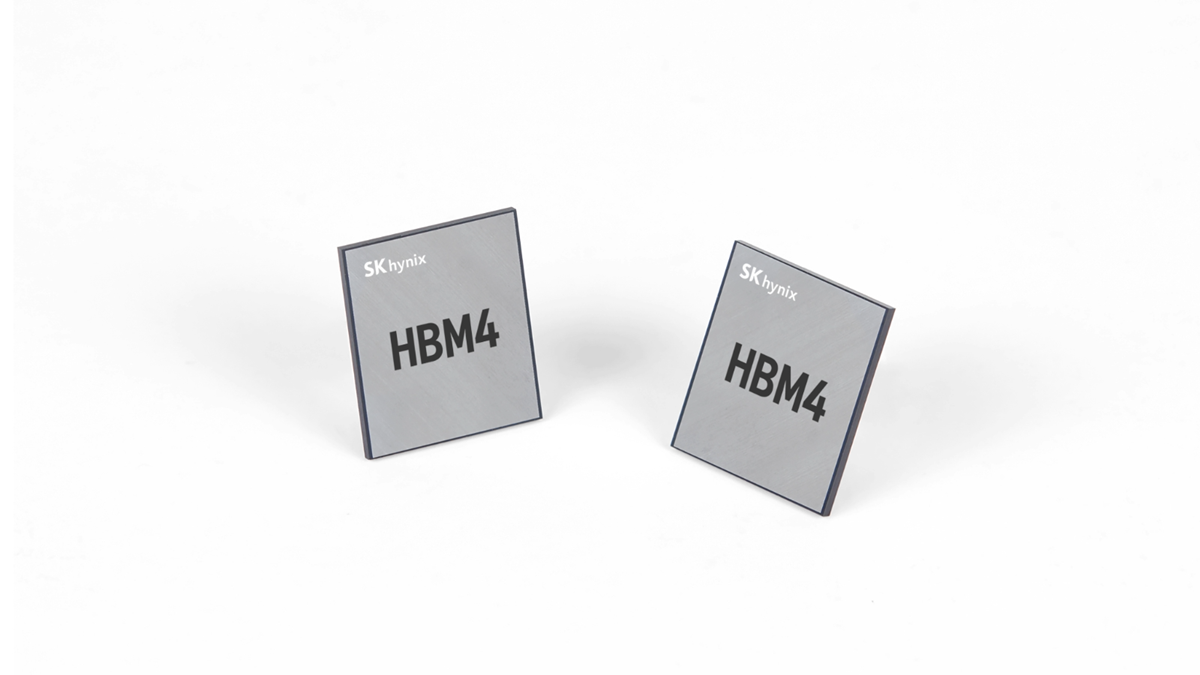

事件總覽:全球固態技術協會(JEDEC)正積極討論放寬HBM4的堆疊高度上限至900微米,這項潛在的重大決議,將為AI記憶體技術發展帶來關鍵突破,直接影響16至20層DRAM堆疊的實現,並牽動全球半導體封裝設備商與記憶體大廠的未來策略佈局。

📅 近期:JEDEC啟動HBM高度標準討論

全球固態技術協會(JEDEC)近期已正式展開一項關鍵討論,計畫放寬全球HBM的堆疊高度標準限制,這直接關係到未來AI運算核心的高效能記憶體發展。這項重大決議預計將HBM4的堆疊高度上限從現行的775微米(約0.075公分),大幅放寬至900微米(約0.09公分),藉此支援針對現代AI功能關鍵的16層及20層DRAM堆疊技術發展。

這背後其實反映了現有製程所面臨的嚴峻物理瓶頸。JEDEC指出,為了在有限高度內塞入更多層記憶體,製造商被迫將矽晶片打磨得極薄,這不僅導致整體生產良率降低,更大幅增加了熱管理(thermal management)的困難度,進而阻礙了技術的推進。將高度上限提升至900微米,意味著業界能夠在維持較佳良率與散熱效果的前提下,順利推進更高層數的AI DRAM堆疊技術,這對記憶體產業來說,無疑是一劑強心針。

📅 2026年:韓國半導體展上的業界觀點

有趣的是,這項垂直高度標準的變更,直接為半導體組裝設備市場帶來了全新的需求與變化。一旦900微米的標準正式獲得批准,記憶體製造商在進行高密度堆疊時,將得以繼續沿用現有的熱壓合機(thermal compression bonders)。這項發展為現有設備龍頭帶來了巨大的市場優勢;據統計,韓美半導體(Hanmi Semiconductor)目前在全球熱壓合設備市場中佔有高達71.2%的市佔率,預計將成為此波標準放寬下的最大受惠者。

在2026年韓國國際半導體展上,SK海力士(SK Hynix)的代表明確指出,放寬高度限制將有助於提升現階段的生產效率,讓他們能更從容地應對市場需求。不過,他們也坦言,當未來堆疊層數超過20層時,混合鍵合技術(hybrid bonding)仍將成為不可或缺的必需品。另一方面,三星電子雖然已經開發出能提供比現有製造方法更佳抗熱性的混合鍵合技術,但為了提升利潤率,該公司仍可選擇繼續使用現有的生產方法。說真的,最終的設備選擇與製程決策,將高度取決於重要客戶的特定效能需求,例如輝達(Nvidia)在設計其GPU封裝時所需的全新HBM模組規格。

至今影響與未來展望

目前,整個半導體產業都在密切關注JEDEC的討論進度,因為最終的決議結果將直接決定哪些設備供應商能在這個十年的末期取得成功。儘管混合鍵合技術能夠實現無凸塊(without bumps)的晶片直接連接,但與傳統的熱壓合方法相比,製造商需要投入更多的資金與時間成本,這也是目前推廣的一大考量。在製造商致力於實現DRAM最大密度的同時,他們的首要任務依然是減少良率損失,以確保成本效益。

根據相關市場專家分析指出,在900微米標準確立與混合鍵合方法完全成熟之間,市場將經歷一段短暫的穩定期,並透過先進的組裝解決方案來維持市場的穩定運作。次世代鍵合技術何時能全面導入規模化量產,最終仍將取決於標準制定機構的規範、設備的精確度,以及全球AI基礎設施的實際需求。這場關於HBM高度標準的辯論,不僅是技術層面的較量,更是產業未來發展方向的風向球。